# DESCRIPTION

The PT2511 is a three-phase, hall sensor sinusoidal brushless DC motor driver with integrated power MOSFETs, which can provide continuous drive current up to 1.5A. The three-phase control is based on sine wave driving scheme and it is designed to reduce electrical audible noise in motor phase commutation. The integrated charge pump of the device boosts VDD internally and fully enhances the high-side MOSFETs. On-chip +5V LDO provide voltage for logic and analog circuits operation. The PT2511 has internal TSD function protection. The package of PT2511 is HTSSOP28.

## **FEATURES**

- Hall sensor sinusoidal control for 3-phase BLDC

- Current limit function

- Drive current: 1.5 A continuous

- Thermal shutdown(TSD) protection

- Motor lock protection

- Forward/Reverse control with FWR pin

- PWM or DC input for speed control

- FG output for rotation speed

- Support Hall element and Hall sensor

- I2C interface for parameter setting and write to internal OTP,

# **APPLICATIONS**

- Three-phase BLDC motor

- Fan application

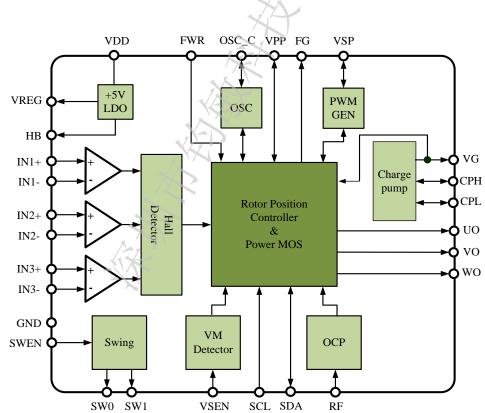

# **BLOCK DIAGRAM**

## **APPLICATION BLOCK DIAGRAM**

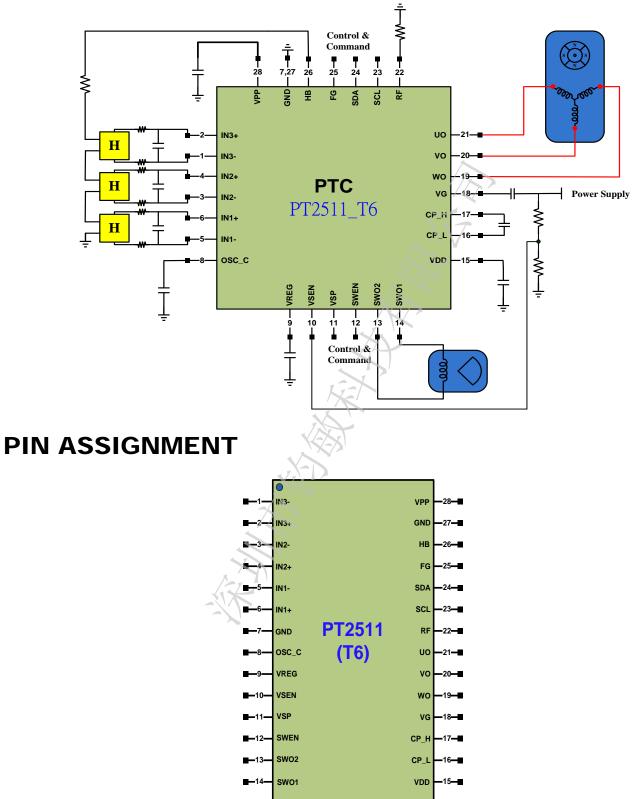

## **PIN DESCRIPTION**

| Pin Name | I/O/P | Description                                                    | Pin No. |

|----------|-------|----------------------------------------------------------------|---------|

| IN3-     | I     | Hall element 3 input-                                          | 1       |

| IN3+     | I     | Hall element 3 input+                                          | 2       |

| IN2-     | I     | Hall element 2 input-                                          | 3       |

| IN2+     | I     | Hall element 2 input+                                          | 4       |

| IN1-     | I     | Hall element 1 input-                                          | 5       |

| IN1+     | I     | Hall element 1 input+                                          | 6       |

| GND      | Р     | Signal ground                                                  | 7,27    |

| OSC_C    | Ι     | Connect to external capacitor for startup step setting         | 8       |

| VREG     | 0     | +5V LDO output                                                 | 9       |

| VSEN     | I     | Connect to voltage divider of VDD for voltage sensing.         | 10      |

| VSP      | I     | DC or PWM input for speed control                              | 11      |

| SWEN     | I     | Swing head enable control; "1" = start motor                   | 12      |

| SWO2     | I/O   | Swing motor control – full-bridge output 2                     | 13      |

| SWO1     | I/O   | Swing motor control - full-bridge output 1                     | 14      |

| VDD      | Р     | VDD supply input                                               | 15      |

| CP_L     | I/O   | Charge pump pin, use a ceramic capacitor between CP_H and CP_L | 16      |

| CP_H     | I/O   | Charge pump pin, use a ceramic capacitor between CP_H and CP_L | 17      |

| VG       | Р     | Charge pump output                                             | 18      |

| WO       | 0     | W phase signal output                                          | 19      |

| VO       | 0     | V phase signal output                                          | 20      |

| UO       | 0     | U phase signal output                                          | 21      |

| RF       |       | Current limit voltage sensing                                  | 22      |

| SCL      |       | Serial clock input - I2C control interface                     | 23      |

| SDA      | 1/0   | Serial data input/output - I2C control interface               | 24      |

| FG       | 0     | Motor rotation speed indicator, logic level output             | 25      |

| НВ       | 0     | Controlled +5V output for Hall sensor bias                     | 26      |

| VPP      | Р     | High voltage power supply (7.5V) for<br>programming OTP        | 28      |

## **FUNCTION DESCRIPTION**

#### POWER SUPPLY

PT2511 consumes very low current (<5mA) and build-in a 5V LDO for logic and analog circuits. The supply voltage for VDD range from +7V to +28V. For lower operation voltage in VDD, the VDD and VREG can be connected together.

PT2511 will detect VREG to reach 3V internally for avoiding instability on external power. A power good signal will send to logic circuit to start operation within 10ms.

Adding proper bypass capacitor(s) close to the sensible IC pins will reduce interference from motor systems or wires connection to improve chip performance.

PT2511 has an integrated charge pump to boost VDD for internal N-N type MOSFET driver.

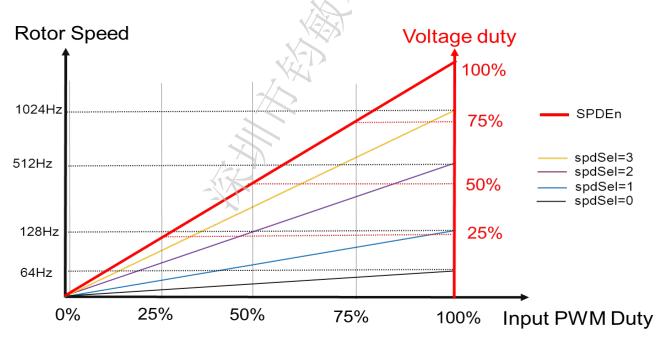

## PWM OR DC INPUT FOR SPEED CONTROL

The PT2511 has an external DC or PWM control input to change the motor speed. For PWM input, the HIGH voltage level needs to be greater than 3.3V(recommended to 3.5V) and the LOW voltage level need to be less than 0.5V(recommended to 0.3V). The PWM carrier frequency is recommended between 15 KHz to 25 KHz. For DC input, the DC control voltage should range from 0.5V to 3.3V.

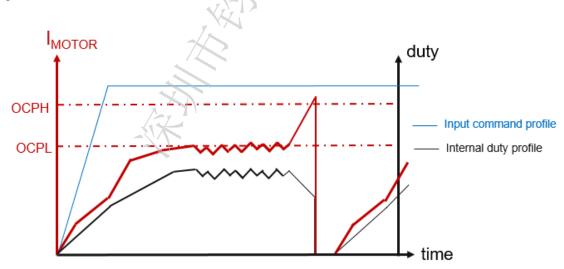

Besides the traditional "duty control voltage" scheme, PT2511 also provide close loop speed control through the setting SpdEN in bit 3 of sub-address 0x39, as depicted in Figure 1. Four slope selections, SpdSel[1:0], are also provide for different motor application. With the help of RiseStep,FallStep1 and FallStep2 parameters, PT2511 provide stable speed regulation output.

**Figure 1**. PT2511 provide different speed control scheme

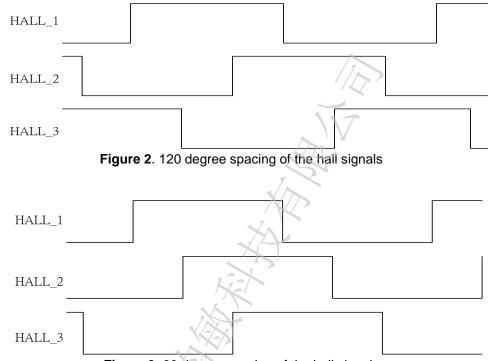

### HALL SENSOR CONTROL SCHEME

The PT2511 control scheme is based on hall sensor information and produce sinusoidal excitation waveform. It benefits to provide accurate and silent (without electrical noise) driving control. Unlike the sensorless control scheme, hall sensor control provides smooth start-up without reverse rotation.

As shown in **Figure 2** and **Figure 3**, three hall sensors can be configured as 60° or 120° spacing through internal parameter, PhCode, 0: 60 degree spacing, 1: 120 degree spacing.

Figure 3. 60 degree spacing of the hall signals

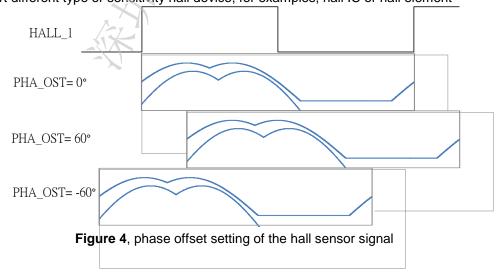

The hall sensor has different sensitivity and layout distance from the rotor to cause phase offset. As shown in **Figure 4**, PT2511 can synchronize the phase offset related to HALL\_U, range from -60 degree to 60 degree through internal parameters, SyncAng and RSyncAng. The phase offset is set individually for the forward or reverse rotation. PT2511 also support different type or sensitivity hall device, for examples, hall IC or hall element

#### PHASE ADVANCE SETTING

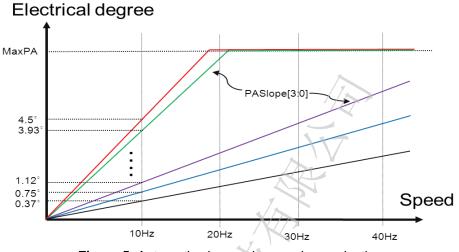

Due to the characteristics of inductance loading of stator winding, the phase of the shunt current may drift away as the rotor speed increase. The PT2511 provide automatic or manual adjustment through the setting PAAuto in address 0x30. It's easy for customer to achieve best efficiency in any circumstance. In the automatic setting, it provides sixteen curves PASlope and one maximum phase leading limitation MaxPA to choose.

Figure 5. Automatic phase advance slope selection

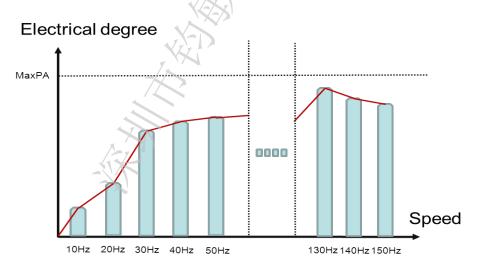

Moreover, the best efficiency point may vary with the intensity of back EMF, shunt current, rotor speed and shunt inductance, etc. With the non-linear characteristic, the parameters of PAM10HZ~PAM150HZ help to adjust phase advance in individual rotation speed manually. The maximum manual adjustment speed is up to 150Hz. And the maximum phase leading limitation MaxPA is also applied in manual mode.

Figure 6. Manual phase advance setting according to speed

### INPUT COMMAND PROFILE

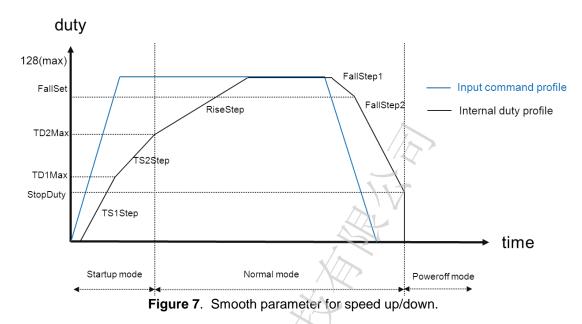

PT2511 provide smooth speed up/down profile with different load as depicted in Figure 7. With the StopDuty setting, user can decide when to release excitation without audible noise.

### **CURRENT PROTECTION**

The PT2511 has a two-level current protection function by using a sense resistor over RF pin and the sensed signal ( $V_{RF}$ ) are related to motor current(Imotor) after low pass filter. When the  $V_{RF}$  exceeds  $V_{OCPL}$ , OCPL signal is triggered, PWM duty will reduce to keep  $V_{RF}$  under  $V_{OCPL}$  threshold. And if the  $V_{RF}$  exceed  $V_{OCPH}$ , OCPH signal is triggered, PWM turnoff and system go into the lock mode.

Figure 8. Two-stage over current protection

The OCPHFilter and OCPLFilter provide deglitch time period ranging from 0.4us to 0.4ms to make sure stable motor operation. Due to the different applications, PT2511 provide multi-level V<sub>OCPL</sub>/V<sub>OCPH</sub> setting through PRT\_LVL register.

### START UP & LOCK PROTECTION

The initial position information is provided by hall sensor. According to hall signal, PT2511 commutates motor and startup. The startup mode maximum duty is set by TD2Max, in other words, the maximum startup force for different motor application. Increasing / decreasing PWM duty, the motor speed can be accelerated/ decelerated. And the profile can be set from parameters.

If the controller did not detect the expected hall sensor signal, the state machine would go to the lock protection mode. PT2511 will wait a period and re-start again (the period and re-start times are set by internal parameter CTRise and CTFall) and the ExptNum exception number counter will plus 1. If the motor remained to be locked, and the counter number exceed the MaxExptNum setting, it would cause system fall into the dead lock status. System no longer start at this state, and the only way to restart the system is turning off then turning on the supply voltage.

### **OVER TEMPERATURE PROTECTION**

PT2511 has an internal thermal shutdown (TSD) protection. It shuts down the chip for junction temperature larger than 155 °C and recovers operating conditions for junction temperature falls back to 115 °C.

## UNDER VOLTAGE AND OVER VOLTAGE PORTECTION

When the voltage level of VSEN pin is greater than (VREG/2) or less than (VREG/2)- $\Delta$ V, the output power MOSFETs are shut down.

The voltage level of  $\Delta V$  is set by OTP(One Time Programming) memory.

## FG OUTPUT FOR SPEED INFORMATION

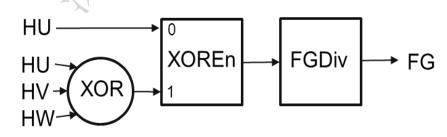

PT2511 has FG output to observe motor speed. When the rotor is running an electric cycle, the FG output toggles High to Low. So when calculating the rotation speed, it needs to take into account the pole numbers of the rotor. For example, if rotor is 8 poles (four pairs of NS), the motor run a lap will have 4 FG output. Motor speed is usually present in RPM (Revolutions per Minute), so the rotation speed of the simple formula is calculated as

RPM = FG x 120 / POLE, FG is frequency in Hz, "POLE" is numbers of rotor.

FG pin is a 5V logic output.

PT2511 provide different FG configuration for external device to access, as the **Figure 11** depicted. XOREn setting enable three times factor and FGDiv provide divided by 1,2,4,8 setting.

Figure 11. FG output configuration

### FORWARD AND REVERSE SETTING

PT2511 can be set to forward or reverse rotation with internal parameter. If the rotation is switched, the motor will stop automatically and rotate with opposite direction. It is also suggested to control the motor speed by monitoring FG signal to optimize the reverse behavior, such as slow down profile or reverse waiting time.

### UPWIND OR DOWNWIND STARTUP SETTING

PT2511 can detect automatically if the motor operate in the upwind or downwind condition. To make sure the motor operate properly the PT2511 brake the motor in the upwind condition until the rotor speed is down to acceptable range. In the downwind condition, PT2511 provide a scheme to adjust the startup duty to make sure the back EMF won't damage the HV device. The startup duty is set according to the rotor speed with scale and an offset value.

StartDudy=(RotorSpeed>>DNWScale) + DNWInit, where ">>" means right shift

### PARAMETERS SETTING

The other parameters are adjustable and wrote to internal OTP(One Time Programming) memory. PT2511 can be programmed two times through the I2C interface. VPP pin need apply +7.5V during the OTP programming.

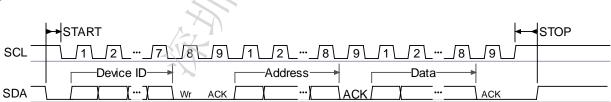

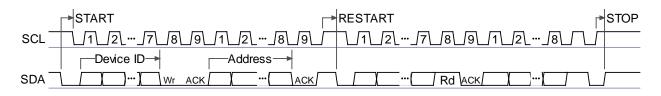

## I<sup>2</sup>C MICROPROCESSOR INTERFACE

To communicate with PT2511, the following control and status registers are accessible via I<sup>2</sup>C interface. I<sup>2</sup>C communicates with multiple devices by only two lines, **START** bit means a start condition; any transmission must start with it. **Device ID** is 7-bit device address identifier, each device owns only one address, and PT2511 is fixed to 0110100b. **Wr**

**Rd** issuing a read or write operation, **ACK** is acknowledge bit, perform in the receiver, to inform the transmitter the data is properly received or stop data transmitting. **Address** is PT2511's register number to be described in next section. **STOP** is stop bit; any sequence must end with it. The I<sup>2</sup>C write operation is byte write mode, and read operation is byte read mode as described in **Figure 12**. The current I<sup>2</sup>C protocol speed support up to 50 KHz.

I2C Byte Write

#### I2C Byte Read

#### Figure 12. I<sup>2</sup>C byte write and byte read timing.

## **REGISTER TABLE**

Register table mapping for address 0x0~0x8

|                                           |                                                                    |        |        |                 | Bit     |        |           |                       |           | Address  |

|-------------------------------------------|--------------------------------------------------------------------|--------|--------|-----------------|---------|--------|-----------|-----------------------|-----------|----------|

| 7                                         | 6                                                                  |        | 5      | 4               | 3       |        | 2         | 1                     | 0         | Hex      |

|                                           |                                                                    | Reser  | ved    |                 |         | Р      | WMS       | FWRS1                 | FWRSØ     | 0        |

|                                           |                                                                    |        |        | PWM_3           | 12C     |        |           |                       |           | 1        |

|                                           | FG_CNT[7:0]                                                        |        |        |                 |         |        |           |                       | 2         |          |

|                                           | M_Status[2                                                         | -      |        | RDL             | TSD     |        | FG_C      | CNT[10:8]             |           | 3        |

|                                           | Reserved         SUMERR         BLANKERR         OCPL         OCPH |        |        |                 |         |        |           |                       | 4         |          |

|                                           |                                                                    |        |        | Reser           |         |        |           |                       |           | 5        |

|                                           |                                                                    |        |        | HVI             |         | 1      | 7         |                       |           | 6        |

|                                           |                                                                    |        |        | EXPNUM          | [7:0]   |        | V         |                       |           | 7        |

|                                           |                                                                    |        |        | Reserved        |         | A      |           |                       | EXPNUM[8  | 8        |

|                                           |                                                                    |        |        | Bit             |         |        |           |                       |           | Address  |

| 7                                         | 6                                                                  | 5      |        | 4 TC1C+++       | 3       | 2      | 1         |                       | 0         | Hex      |

|                                           |                                                                    |        |        | TS1Step<br>TD2M |         |        |           |                       |           | 21       |

| [S1Step[8]                                | DNWScale                                                           | -[1:0] |        |                 |         | TD1Ma> | <u> </u>  |                       |           | 22<br>23 |

|                                           |                                                                    | -[]    |        | TS2Step         | 7:0]    |        | -         |                       |           | 24       |

|                                           |                                                                    |        |        | RiseStep        |         |        |           |                       |           | 25       |

|                                           |                                                                    | DNWI   | nit[5: | 0]              |         |        | TS2Step   | [8] Ris               | eStep[8]  | 26       |

|                                           |                                                                    |        | 4      | FallStep        | 1[7:0]  |        |           |                       |           | 27       |

|                                           |                                                                    |        |        | FallStep        | 2[7:0]  |        |           |                       |           | 28       |

|                                           | Reserved                                                           |        | 12     | Dead            | dTime   |        | FallStep: | <mark>1[8]</mark> Fal | lStep2[8] | 29       |

|                                           |                                                                    |        | -      | Falls           |         |        |           |                       |           | 2A       |

|                                           |                                                                    |        |        | StopD           | uty     |        |           |                       |           | 2B       |

|                                           | Resei                                                              | rved   |        |                 |         | Z      | CTarget   |                       |           | 2C       |

|                                           |                                                                    |        |        | Reser           |         |        |           |                       |           | 2D       |

| Filter                                    | Max[9:8]                                                           |        |        |                 |         | erved  |           |                       |           | 2E       |

|                                           |                                                                    | long   |        | FilterMa        | x[/:0]  |        |           |                       |           | 2F       |

| HallPwrEn OCPLSlope PAAuto PASlope        |                                                                    |        |        |                 |         |        | 30        |                       |           |          |

| HallSel   RSyncAng     Reserved   SyncAng |                                                                    |        |        |                 |         |        | 31        |                       |           |          |

| reserved                                  | CTR:                                                               | ico    |        |                 | SyncAng |        | CTFall    |                       |           | 32       |

|                                           | CTR.                                                               | 156    |        | MaxExptNu       | Im[7·0] |        | CIFAII    |                       |           | 33       |

|                                           |                                                                    |        |        | Πάλεχμείου      | ,       |        |           |                       |           | 34       |

|          |                   |               | Reserved             |          |          |          |  |

|----------|-------------------|---------------|----------------------|----------|----------|----------|--|

| Reserved | MaxExptNum<br>[8] |               | R                    | leserved |          |          |  |

|          |                   |               | Reserved             |          |          |          |  |

|          |                   |               | Reserved             |          |          |          |  |

| HSMOS    | HallCode          | Reserved      | SPDEN                | Reserved | SF       | DSEL     |  |

| Reserved |                   |               |                      |          |          |          |  |

|          |                   |               | MaxPA                |          |          |          |  |

|          |                   |               | PAM10Hz              |          |          |          |  |

|          |                   |               | PAM20Hz              |          | <u> </u> |          |  |

|          |                   |               | PAM30Hz              |          |          |          |  |

|          |                   |               | PAM40Hz              |          |          |          |  |

|          |                   |               | PAM50Hz              |          | V        |          |  |

|          |                   |               | PAM60Hz              |          |          |          |  |

|          |                   |               | PAM70Hz              |          |          |          |  |

|          |                   |               | PAM80Hz              |          |          |          |  |

|          |                   |               | PAM90Hz              |          |          |          |  |

|          |                   |               | PAM100Hz<br>PAM110Hz | 4        |          |          |  |

|          |                   |               | PAMII0HZ<br>PAM120Hz | <u> </u> |          |          |  |

|          |                   |               | PAM120H2             |          |          |          |  |

|          |                   |               | PAM140Hz             |          |          |          |  |

|          |                   |               | PAM150Hz             |          |          |          |  |

| Res      | erved             |               |                      | CLKTrim  |          |          |  |

|          |                   |               | PRT_LVL              |          |          |          |  |

|          |                   | -OCP          | HFLTR[7:0]           |          |          |          |  |

|          |                   | OCPLFLTR[5:0] |                      |          | OCPHF    | LTR[9:8] |  |

| UF       | WSel              |               | R                    | leserved |          |          |  |

|          |                   | UF            | WNUM[7:0]            |          |          |          |  |

| Reserved |                   | A REAL        | MinDut               | V        |          |          |  |

| FWRSW    |                   | Reserved      | OVOTSEL              |          | Reserved |          |  |

|          |                   | Reserved      |                      | F        | GDIV     | XOREN    |  |

## **REGISTER DESCRIPTION**

Address 0x0~0x8 is system control registers, providing information such as system status, even direct control the PWM duty, forward or reverse, etc.

| Address | Register<br>Name |            | Description                                                                                                                                                                                          | Default | Unit    | R/W |

|---------|------------------|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|---------|-----|

|         |                  | Bit [7:3]  | Reserved                                                                                                                                                                                             |         |         |     |

| 0x00    | SYS_CTL1         | Bit[2]     | PWMS :<br>1 : select internal PWM duty control<br>0 : external VSP control                                                                                                                           | 0       |         | R/W |

|         |                  | Bit[1:0]   | FWRS : FWR is controlled by<br>1x : external FWR pin<br>$00_b : FWR is 0$<br>$01_b : FWR is 1$                                                                                                       | 2       |         |     |

| 0x01    | PWM_I2C          | When PV    | VMS set 1, PWM duty is controlled by this register                                                                                                                                                   | 0       | duty    | R/W |

| 0x02    | FG_CNT[7:0]      |            | FG_CNT[10:8] to get a 11 bit frequency counter ery one second                                                                                                                                        | 0       | counter | R   |

|         |                  | Bit[7:5]   | M_Status, Motor status<br>$000_b$ : Startup<br>$001_b$ : Normal<br>$010_b$ : PWMOff<br>$100_b$ : LockOn<br>$101_b$ : DeadLock                                                                        |         |         |     |

| 0x03    | SYS_CTL2         | Bit[4]     | RDL, normal operation status<br>0 : motor is in the normal state<br>1 : motor is not in the normal state                                                                                             |         |         | R   |

|         |                  | Bit[3]     | TSD signal from the VSEN pin<br>0 : Comparator result is correct<br>1 : Comparator result is not correct                                                                                             |         |         |     |

|         |                  | Bit[2:0]   | FG_CNT[10:8]                                                                                                                                                                                         |         |         |     |

|         |                  | Bit[7:5] 🗸 | Reserved                                                                                                                                                                                             |         |         |     |

|         |                  | Bit[4]     | SUMERR, OTP checksum error indicator. If the first<br>byte is 0x5A, the checksum is generated<br>automatically.<br>1 : OTP checksum is error<br>0 : OTP checksum is correct.                         |         |         |     |

| 0x04    | SYS_CTL3         |            | BLANKERR, OTP blanking check.<br>00 : Bank 0 and 1 is blank.<br>01 : Bank 0 is blank, bank 1 is not blank.<br>10 : Bank 0 is not blank, bank 1 is blank.<br>11 : Bank 0 and 1 is not blank.<br>OCPL, |         |         | R   |

|         |                  | Bit[1]     | <ol> <li>1 : RF pin voltage exceed low level threshold.</li> <li>0 : RF pin voltage is under low level threshold.</li> </ol>                                                                         |         |         |     |

| Address | Register<br>Name |          | Description                                                                                                                                      | Default | Unit | R/W |

|---------|------------------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------|---------|------|-----|

|         |                  | Bit[0]   | OCPH<br>1 : RF pin voltage exceed high level threshold.<br>0 : RF pin voltage is under high level threshold.                                     |         |      |     |

| 0x06    | HVID             | Hardware | e version control ID                                                                                                                             | 2       |      | R   |

| 0x07    | EXPTNUM<br>[7:0] | The EXF  | with EXPTNUM[8] to get a EXPTNUM[8:0] register.<br>PTNUM will add one automatically when exception<br>for example, OCPH or LockOn state happens. | 0       |      | R   |

| 0x08    |                  | Bit[7:1] | Reserved                                                                                                                                         |         |      |     |

| 0,000   |                  | Bit[0]   | EXPTNUM[8]                                                                                                                                       | 0       |      | R   |

#### Address 0x21~0x5F is OTP parameters mapping registers, provide motor control related parameters.

| Address | Register<br>Name    |                                 | Description                                                                                                                                                    | Default | Unit  | R/W |

|---------|---------------------|---------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|-------|-----|

| 0x21    | TS1Step             | TS1Step[<br>TS1Step             | with bit 7 of sub-address 0x23 to form 9-bit of<br>8:0]<br>is the first stage slope before reaching TD1MAX in the<br>ode. Please refer to Figure 7. Unit is ms | 10      | ms    | R/W |

| 0x22    | TD2Max              | TD2Max                          | is the maximum duty of the second stage startup.<br>fer to Figure 7                                                                                            | 50      | duty  | R/W |

|         |                     | bit [7]                         | TS1Step[8]                                                                                                                                                     |         |       |     |

| 0x23    | TD1Max              | bit[6:5]                        | DNWScale[1:0], a scale of current speed in Hz, for example, the current speed is 48Hz, DNWScale set to 0, then the initial duty is startup from 48>>(0+2)      | 0       | scale | R/W |

|         |                     | bit[4:0]                        | TD1Max is the maximum duty of the first stage startup. Please refer to Figure 7.                                                                               | 3       | duty  |     |

| 0x24    | TS2Step             | TS2Step[<br>TS2Step             | with bit 1 of sub-address 0x26 to form 9-bit of<br>8:0]<br>is the second stage slope before reaching TD2MAX in<br>p mode. Please refer to Figure 7.            | 47      | ms    | R/W |

| 0x25    | RiseStep            | Combine<br>RiseStep<br>RiseStep | with bit 0 of sub-address 0x26 to form 9-bit of                                                                                                                | 47      | ms    | R/W |

| 0x26    | Downwind<br>startup | bit [7:2]<br>bit [1]            | DNWInit[5:0], Combine with DNWScale[1:0], a suitable initial force to startup the motor when motor in a forward running situation.<br>TS2Step[8]               | 0       | duty  | R/W |

|         |                     | bit [0]                         | RiseStep[8]                                                                                                                                                    |         |       |     |

| 0x27    | FallStep1           | The first to Fallse             | stage slope of slow down before the actual duty down t.                                                                                                        | 47      | ms    | R/W |

| 0x28    | FallStep2           |                                 | ond stage slope of slow down before the actual duty StopDuty                                                                                                   | 47      | ms    | R/W |

|         |                     | Bit[7:5]                        | Reserved                                                                                                                                                       |         |       |     |

| 0x29    | DeadTime<br>Setting | Bit[4:2]                        | Dead time setting, range from 0.4us to 2.4us, suit for wide voltage operation.<br>0: 0.4us, 1: 0.8us, 2: 1.2us, 3: 1.6us, 4: 2.0us, 5~7: 2.4us                 |         | clock | R/W |

|         | _                   | bit [1]                         | FallStep1[8]                                                                                                                                                   |         |       |     |

|         |                     | bit [0]                         | FallStep2[8]                                                                                                                                                   |         |       |     |

| 0x2A    | FallSet             | The first                       | stage duty for the actual duty decrease to.                                                                                                                    | 40      | duty  | R/W |

| 0x2B    | StopDuty            | The sec                         | ond stage duty for the actual duty decrease to.                                                                                                                | 64      | duty  | R/W |

| Address | Register<br>Name  |            | Description                                                                                                                                                                                                                                                                                                              | Default | Unit    | R/W   |     |

|---------|-------------------|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|---------|-------|-----|

| 0.420   | ZOTorgot          | Bit[7:4]   | Reserved                                                                                                                                                                                                                                                                                                                 | C       | alaak   |       |     |

| 0x2C    | ZCTarget          | Bit[3:0]   | Six-step startup count before entering normal state                                                                                                                                                                                                                                                                      | 6       | clock   | R/W   |     |

| 0x2E    | E FilterMax       | Bit[7:6    | Bit[7:6] FilterMax[9:8]                                                                                                                                                                                                                                                                                                  |         | 0       | clock | R/W |

| UXZE    | Filleriviax       | Bit[5:0]   | Reserved                                                                                                                                                                                                                                                                                                                 | 0       | CIUCK   |       |     |

| 0x2F    | FilterMax         | FilterMax  | is the deglitch time period both for the hall sensor/hall                                                                                                                                                                                                                                                                | 100     | clock   | R/W   |     |

|         |                   | Bit[7]     | HallPwrEn, HB power output control<br>0: Turn off HB output during power-off mode,<br>1: HB output is always enable.                                                                                                                                                                                                     | 0       |         |       |     |

|         |                   | Bit[6:5]   | OCPLSlope, OCPL update rate selection when the<br>OCPL event happens.<br>0: 6ms, 1: 12ms, 2:23ms, 4:47ms                                                                                                                                                                                                                 | 2       |         |       |     |

| 0x30    | PASlope           | Bit[4]     | PAAuto, Phase leading adjustment selection,<br>0: manually, 1: auto                                                                                                                                                                                                                                                      | 1       |         | R/W   |     |

|         | E                 |            | PASlope, when PAAuto set to 1, there are 16 slope<br>curves selection according to the rotation speed.<br>Please check figure 5 and 6 for further explanation.<br>The sixteen slope of phase advance per 10Hz is 4.5,<br>3.93, 3.56, 3.18, 3.0, 2.8, 2.6, 2.43, 2.25, 2.06, 1.87,<br>1.68, 1.5, 1.12, 0.75, 0.37 degree. | 7       |         |       |     |

|         |                   | Bit[7]     | HallSel, Hall effect sensor type selection<br>0:Hall sensor IC, 1: Hall element                                                                                                                                                                                                                                          | 0       |         |       |     |

| 0x31    | RSyncAng          | Bit[6:0]   | Hall sensor synchronization angle for the reversion rotation.                                                                                                                                                                                                                                                            | 45      | 1.5 deg | R/W   |     |

| 0x32    | SyncAng           | Bit[6:0]   | Hall sensor synchronization angle for the forward rotation                                                                                                                                                                                                                                                               | 45      | 1.5 deg | R/W   |     |

| 0x33    | CTRise<br>/CTFall | Bit[7:4]   | Maximum time period before entering normal mode. If startup period exceed this period, lock-on number plus one and restart again.                                                                                                                                                                                        | 2       | sec.    | R/W   |     |

|         |                   | Bit[3:0]   | Rest time period between each startup.                                                                                                                                                                                                                                                                                   | 1       | sec.    |       |     |

| 0x34    | MaxExptNum        | state. The | kimum exception number before entering dead-lock<br>e exception include OCPH and lock-on. When entering<br>k state, PT2511 release it only by system power on                                                                                                                                                            | 20      | times   | R/W   |     |

|         |                   | Bit[7]     | HSMOS, high side MOS type selection<br>0:NMOS, 1:PMOS                                                                                                                                                                                                                                                                    | 0       |         |       |     |

|         | 0x39 SPDCtrl      | Bit[6]     | HallCode, Hall effect sensor position<br>0: 60 degree spacing, 1: 120 degree spacing                                                                                                                                                                                                                                     | 0       |         |       |     |

| 0x39    |                   | Bit[3]     | SpdEn : 0: duty control voltage, 1: duty control speed, please check figure 1                                                                                                                                                                                                                                            | 0       |         | R/W   |     |

|         |                   | Bit[1:0]   | SpdSel, four different slope curve to choose maximum<br>rotation speed<br>0:64Hz, 1: 128Hz, 2:512Hz, 3:1024Hz,<br>please check Figure 1 for further explanation.                                                                                                                                                         | 2       |         |       |     |

| Address       | Register<br>Name     |                                                                                                                                    | Description                                                                                                                                                                        | Default                                                  | Unit     | R/W          |

|---------------|----------------------|------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|----------|--------------|

| 0x3B          | MaxPA                | Maximur                                                                                                                            | n phase advance limitation                                                                                                                                                         | 30                                                       | 1.5 deg. | R/W          |

| 0x3C~<br>0x4A | PAM10HZ~<br>PAM150HZ |                                                                                                                                    | advance adjusted manually from 10Hz to 150Hz<br>g the rotation speed.                                                                                                              | 2,4,6,8,1<br>0,12,13,<br>15,17,18<br>,20,21,2<br>3,24,25 | 1.5 deg  | R/W          |

| 0x4B          | CLKTrim              | CLKTrim                                                                                                                            | [5:0] provide 6 bit for precise basic clock output.                                                                                                                                | 35                                                       | level    | R/W          |

|               |                      | Bit[7:4]                                                                                                                           | Over voltage/temperature protection level(VPRTL) selection, range from 1.0V~2.24V(0x0~0xE), 15 level settings.                                                                     | 0xD                                                      |          | <b>D</b> 444 |

| 0x4C          | PRT_LVL              | Bit[3:0]                                                                                                                           | Over current protection level(OCPL/OCPH) selection, range from 0.16V/0.26V to 0.41V/0.69V, 16 level settings.                                                                      | 0x0                                                      | level    | R/W          |

| 0x4D          | OCPHFiltr<br>[9:0]   |                                                                                                                                    | with bit[1:0] of sub-address 0x4E, to form 10-bit of time period for the OCPH signal, range from 0.4us to                                                                          | 256                                                      | clock    | R/W          |

| 0x4E          | OCPLFiltr<br>[5:0]   | Bit[7:2]<br>Bit[1:0]                                                                                                               | Deglitch time period for the OCPL signal, range from 0.4us to 25.6us.<br>OCPHFiltr[9:8]                                                                                            | 8                                                        | clock    | R/W          |

| 0x4F          | UWSel                | Bit[7:6]                                                                                                                           | UPWSel : Upwind startup setting, the motor brake until<br>the speed reach: 0:4Hz, 1:6Hz, 2:8Hz, 3:12Hz, then<br>start up with six-step till the motor in the forward<br>direction. | 0                                                        |          | R/W          |

| 0x50          | UPWNum               |                                                                                                                                    | Reserved<br>n add 1 if the low-side braking time exceed<br>n*0.5 second                                                                                                            | 20                                                       | number   | R/W          |

| 0x51          | MDuty                | Bit[7]<br>Bit[6:0]                                                                                                                 | Reserved<br>MinDuty : The motor is activated until the duty setting<br>exceed MinDuty                                                                                              | 0                                                        | duty     | R/W          |

| 0x52          | OVOTSEL/             | FWRSW, direct set PT2511 to 0: forward rotation, 1:           Bit[7]         reverse rotation in the 28 pin SSOP package, This bit |                                                                                                                                                                                    | 0                                                        |          | R/W          |

|               | FWRSW                | Bit[4]                                                                                                                             | OVOTSEL, 1: over temperature selection, 0: over voltage selection.                                                                                                                 | 0                                                        |          | 1.7.7.7      |

| 0x53          | FGCTRL               | Bit[7:3]<br>Bit[2:1]                                                                                                               | Reserved<br>FGDiv : FG divide setting,<br>00b:1, 01b:2, 10b:4, 11b:8                                                                                                               | 00 <sub>b</sub>                                          |          | R/W          |

|               |                      | Bit[0]                                                                                                                             | XOREn : FG XOR enable setting,<br>0:disable, 1:enable                                                                                                                              | Ob                                                       |          |              |

## **ABSOLUTE MAXIMUM RATINGS**

| Parameter                   | Symbol           | Min. | Max. | Unit |

|-----------------------------|------------------|------|------|------|

| Supply voltage range        | V <sub>DD</sub>  | 5    | 30   | V    |

| I/O voltage                 | -                | -0.3 | 5    | V    |

| Operating temperature range | TA               | -40  | +85  | °C   |

| Storage temperature range   | T <sub>STG</sub> | -55  | +125 | °C   |

## **ELECTRICAL CHARACTERISTICS**

Nominal conditions:  $V_{DD} = 24.0V$  GND=0 T<sub>A</sub> = +27°C

| Parameter                                                             | Symbol            | Conditions                                   | Min. | Тур. | Max.                   | Unit |

|-----------------------------------------------------------------------|-------------------|----------------------------------------------|------|------|------------------------|------|

| General Characteristics                                               |                   | · · · ·                                      |      |      |                        |      |

| Supply voltage                                                        | Vdd               |                                              | 7    | 24   | 28                     | V    |

| Current consumption                                                   | IDD               |                                              |      | 5    | 8                      | mA   |

| Regulator output voltage*                                             | $V_{REG}$         |                                              | 4.98 | 5    | 5.02                   | V    |

| Regulator output current                                              | I <sub>REG</sub>  | (V_noload - V_load20ma)/<br>V_noload < 5%    |      | 20   |                        | mA   |

| Parameters Setting                                                    |                   | 1                                            |      |      |                        |      |

| Low protection voltage**                                              | Vprtl             | VSEN pin                                     | 2    | 2.0  |                        | V    |

| High protection voltage                                               | Vprth             | VSEN pin                                     | 2.0  | 2.5  |                        | V    |

| Over current protection voltage level<br>low (OCPL, current limit)*** | V <sub>OCPL</sub> | RF pin                                       |      | 0.15 |                        | V    |

| Over current protection voltage level<br>high (OCPH, lock protection) | Vocph             | RF pin                                       |      | 0.24 |                        | V    |

| External oscillator                                                   | Fosc_1ĸ           | OSCC= 470pF                                  |      | 1    |                        | KHz  |

| External oscillator range                                             | Fosc_c            | OSCC pin                                     | 0.1  | -    | 10                     | KHz  |

| Integrated MOSFET                                                     |                   |                                              |      |      |                        |      |

| RDSON Series resistance (HS + LS)                                     | Rdson             | VDD = 24 V; VG = 28.5 V;<br>lout = 1 A       |      | 0.45 |                        | Ω    |

| Swing-head Driver Characteristics                                     |                   |                                              |      |      |                        |      |

| Voltage drop in full bridge driver                                    |                   | SWO1, SWO2, V <sub>DD</sub> =15V,<br>I=200mA |      | 1    | 2                      | V    |

| Hall Element Amplifier Characterist                                   | ics               |                                              |      |      |                        |      |

| Common-mode input range                                               | V <sub>HCM</sub>  | Using hall element                           | +0.5 |      | V <sub>REG</sub> - 0.5 | V    |

| Hall input sensitivity                                                | Vhsen             |                                              |      | 80   |                        | mV   |

| HB output voltage                                                     | Vнв               | Iнв= 10mA                                    | 4.5  |      |                        | V    |

| I/O Interface                                                         |                   |                                              |      |      |                        |      |

| Logic output high level                                               | Vон               | FG, RD                                       | 4.0  | 4.5  | 5.5                    | V    |

| Logic output low level                                                | Vol               | FG, RD                                       |      | 0    | 0.3                    | V    |

| DC for speed control input range                                      | VDC               | DC input (VSP pin)                           | 0.5  |      | 3.3                    | V    |

| PWM input high level                                                  | VPWMH             | PWM input (VSP pin)                          | 3.5  |      |                        | V    |

| PWM input low level                                                   | VPWML             | PWM input (VSP pin)                          |      |      | 0.3                    | V    |

| PWM input clock                                                       | FPWM_IN           | PWM input (VSP pin)                          | 15   | 20   | 25                     | KHz  |

| THERMAL SHUTDOWN                                                      |                   |                                              |      |      |                        |      |

| Shutdown temperature                                                  | TSDN              |                                              |      | 155  |                        | °C   |

| Hysteresis window                                                     | TSDN_HYS          |                                              |      | 40   |                        | °C   |

\* V<sub>REG</sub> is adjustable with I<sup>2</sup>C interface.

\*\*High and Low protection voltage can be worked as OVP(Over Voltage Protection) trigger voltage, and it is adjustable with I<sup>2</sup>C interface

\*\*\*V<sub>OCPH</sub>, V<sub>OCPL</sub> is adjustable with I<sup>2</sup>C interface

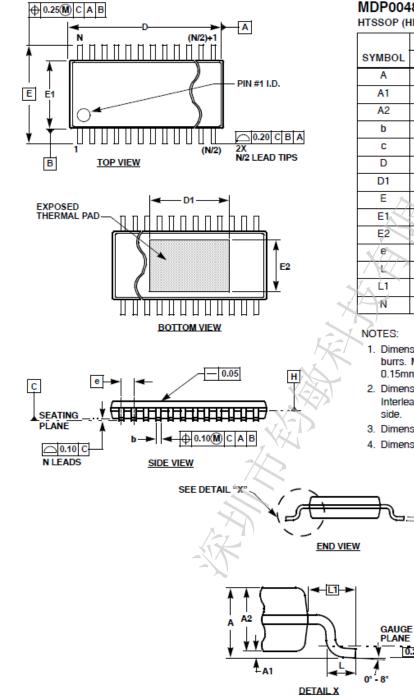

#### PACKAGE INFORMATION 28 Pins, HTSSOP 173MIL

#### **MDP0048** HTSSOP (HEAT-SINK TSSOP) FAMILY

|        |        | MIL   | LIMETE | RS    |       |               |

|--------|--------|-------|--------|-------|-------|---------------|

| SYMBOL | 14 LD  | 20 LD | 24 LD  | 28 LD | 38 LD | TOLERANCE     |

| Α      | 1.20   | 1.20  | 1.20   | 1.20  | 1.20  | Max           |

| A1     | 0.075  | 0.075 | 0.075  | 0.075 | 0.075 | ±0.075        |

| A2     | 0.90   | 0.90  | 0.90   | 0.90  | 0.90  | +0.15/-0.10   |

| b      | 0.25   | 0.25  | 0.25   | 0.25  | 0.22  | +0.05/-0.06   |

| С      | 0.15 / | 0,15  | 0.15   | 0.15  | 0.15  | +0.05/-0.06   |

| D      | 5.00   | 6.50  | 7.80   | 9.70  | 9.70  | <u>+</u> 0.10 |

| D1     | 3.2    | 4.2   | 4.3    | 5.0   | 7.25  | Reference     |

| E      | 6.40   | 6.40  | 6.40   | 6.40  | 6.40  | Basic         |

| E1     | 4.40   | 4.40  | 4.40   | 4.40  | 4.40  | <u>+</u> 0.10 |

| E2     | 3.0    | 3.0   | 3.0    | 3.0   | 3.0   | Reference     |

| e      | 0.65   | 0.65  | 0.65   | 0.65  | 0.50  | Basic         |

|        | 0.60   | 0.60  | 0.60   | 0.60  | 0.60  | <u>+</u> 0.15 |

| ( L1   | 1.00   | 1.00  | 1.00   | 1.00  | 1.00  | Reference     |

| N      | 14     | 20    | 24     | 28    | 38    | Reference     |

| 2      |        |       |        |       |       | Rev. 3 2/07   |

1. Dimension "D" does not include mold flash, protrusions or gate burrs. Mold flash, protrusions or gate burrs shall not exceed 0.15mm per side.

2. Dimension "E1" does not include interlead flash or protrusions. Interlead flash and protrusions shall not exceed 0.25mm per

3. Dimensions "D" and "E1" are measured at Datum Plane H.

4. Dimensioning and tolerancing per ASME Y14.5M-1994.

Notes :

1. Refer to JEDEC MO-137

2. Unit : mm

#### IMPORTANT NOTICE

Princeton Technology Corporation (PTC) reserves the right to make corrections, modifications, enhancements, improvements, and other changes to its products and to discontinue any product without notice at any time. PTC cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a PTC product. No circuit patent licenses are implied.

Princeton Technology Corp. 2F, 233-1, Baociao Road, Sindian, Taipei 23145, Taiwan Tel: 886-2-66296288 Fax: 886-2-29174598 http://www.princeton.com.tw

#### **REVISION HISTORY**

| Date       | Revision      | Modification                                                                                                                                                                                                                                     | Author  |

|------------|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

| 08/10/2016 | PT2501 PRE1.2 | <ol> <li>Add OVP/OTP/OCP description and registers.</li> <li>VOCPL from 0.3 to 0.16, VOCPH from 0.5 to 0.26</li> <li>Add 0x0~0x8 registers description</li> <li>Add I2C diagram and timing as PT2502</li> <li>Update some analog spec</li> </ol> | Vincent |

| 08/12/2016 | REF 1.0       | <ol> <li>Reference from PT2501 PRE1.2</li> <li>Initial Version of PT21511</li> </ol>                                                                                                                                                             | Warren  |

|            |               |                                                                                                                                                                                                                                                  |         |

<u>21.</u>